- Main

- Engineering

- Verilog HDL Design Examples

Verilog HDL Design Examples

Joseph CavanaghThe Verilog language provides a means to model a digital system at many levels of abstraction from a logic gate to a complex digital system to a mainframe computer. The purpose of this book is to present the Verilog language together with a wide variety of examples, so that the reader can gain a firm foundation in the design of the digital system using Verilog HDL. The Verilog projects include the design module, the test bench module, and the outputs obtained from the simulator that illustrate the complete functional operation of the design. Where applicable, a detailed review of the theory of the topic is presented together with the logic design principles―including: state diagrams, Karnaugh maps, equations, and the logic diagram. Numerous examples and homework problems are included throughout. The examples include logical operations, counters of different moduli, half adders, full adders, a carry lookahead adder, array multipliers, different types of Moore and Mealy machines, and arithmetic logic units (ALUs).

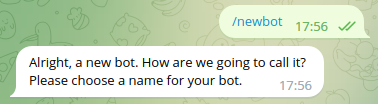

该文件将通过电报信使发送给您。 您最多可能需要 1-5 分钟才能收到它。

注意:确保您已将您的帐户链接到 Z-Library Telegram 机器人。

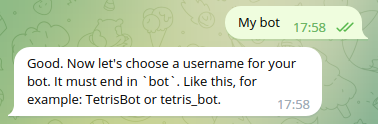

该文件将发送到您的 Kindle 帐户。 您最多可能需要 1-5 分钟才能收到它。

请注意:您需要验证要发送到Kindle的每本书。检查您的邮箱中是否有来自亚马逊Kindle的验证电子邮件。

关键词

关联书单

Amazon

Amazon  Barnes & Noble

Barnes & Noble  Bookshop.org

Bookshop.org  转换文件

转换文件 更多搜索结果

更多搜索结果 其他特权

其他特权